はじめに

私はいつもFPGAのロジックをSystemVerilogやVerilogで記述しています。しかし、Formatterをほとんど使っていませんでした。Pythonとかを書いている時はBlack等のFormatterがあるため、Spaceをそろえたりするところに労力を使わなくても良かったですが、HDLを書いている時はできるだけ綺麗にするために、Spaceを手でそろえていたりしていました。

今回ようやく探してみようと決意したので、使い方や使ってみた感想などを書いておきます。

今回使ってみたのは、veribleです。オープンソースで無償で使えます。ライセンスはApache License 2.0。

参考記事

Formatter(とLanguage Support)の使い方等 (verible formatter, VSCode)

目標は、VSCode上でverible Formatterを使って保存時にコードをフォーマットすることです。またあわよくば、Linterとかもエディター上でかけられて、マウスオーバーでエラーを見ることができたら最高と思ってます。

使用ツール

下記の三つです。

verible

VSCode拡張機能2つ

- SystemVerilog – Language Support – Visual Studio Marketplace

- Verilog-HDL/SystemVerilog/Bluespec SystemVerilog – Visual Studio Marketplace

veribleのFormatterを使うだけなら、SystemVerilog – Language Support – Visual Studio Marketplaceで良いかもです。

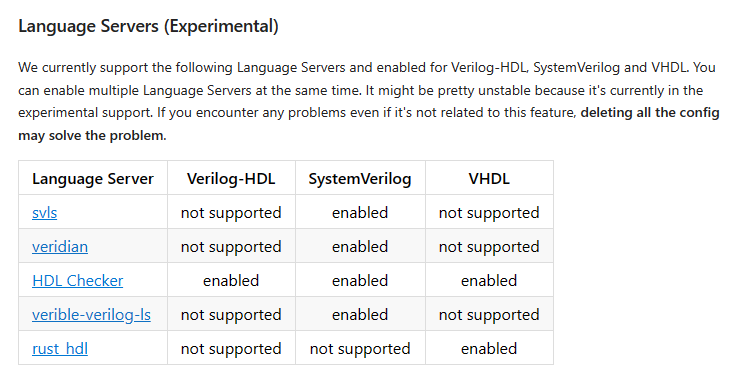

veribleのverible-verilog-lsというLanguage Supportも使いたかったので、Verilog-HDL/SystemVerilog/Bluespec SystemVerilog – Visual Studio Marketplaceも。(まあもともとこれだけは使ってたので)

Formatter(とLanguage Support)を使うために何をすればいいか?

- veribleのバイナリファイルをインストールして、適当なところに置く。

- VSCodeの拡張機能をふたつインストールする。

- 下記をVSCodeの

setting.jsonに記載する。

{

// 拡張機能 Verilog-HDL/SystemVerilog/Bluespec SystemVerilog の設定

// Language Server (verible-verilog-ls)

"verilog.languageServer.veribleVerilogLs.enabled": true,

"verilog.languageServer.veribleVerilogLs.path": "<veribleまでのパス>\\verible-v0.0-3622-g07b310a3-win64\\verible-verilog-ls.exe",

// 拡張機能 SystemVerilog - Language Support の設定

// Formatter & (Language Serverも? ;とかが抜けてるとメッセージをだしてくれる)

"systemverilog.compilerType": "Verible",

"systemverilog.formatCommand": "<veribleまでのパス>\\verible-v0.0-3622-g07b310a3-win64\\verible-verilog-format.exe --indentation_spaces=4",

"[systemverilog]": {

"editor.defaultFormatter": "eirikpre.systemverilog"

},

"[verilog]": {

"editor.defaultFormatter": "eirikpre.systemverilog"

},

// Editor の設定

"editor.formatOnSave": true,

}- ちなみに

"editor.formatOnSave": true,は今回とは特に関係ないですが、ファイルをセーブした時に既定のフォーマッターを適用させる設定です。 - 既定のFormatterをSystemVerilog – Language Supportにしておく。

- Formatterのオプションは

systemverilog.formatCommandでカスタマイズが可能。オプションに関して日本語で説明されている記事は下記がわかりやすいです。後は、元のリファレンスですね。 - 完了です。

使用感

SystemVerilog (.sv)

- verible Formatterはいい感じに使えそうです。

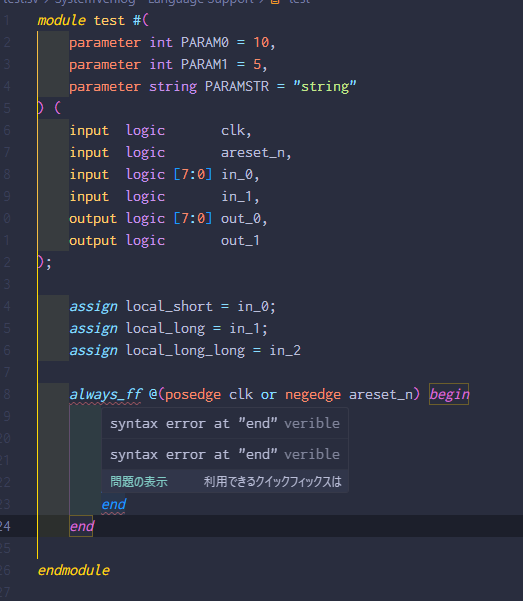

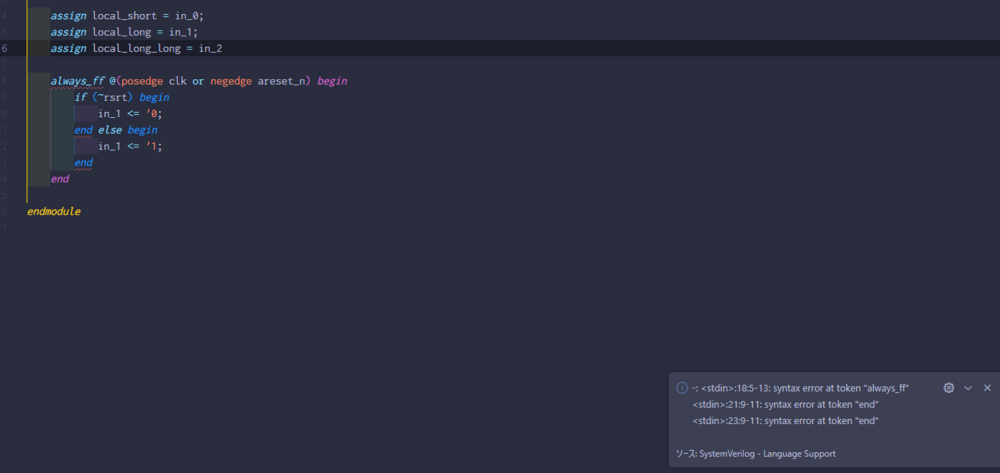

- Language Supportが何なのかあんまり理解できてないですが、セミコロンとかが抜けてるとクイックフィックスを出してくれるのは結構便利です(Verilog-HDL/SystemVerilog/Bluespec SystemVerilog – Visual Studio Marketplaceの機能)

- Vivadoとかの開発環境のエディターで見たときは警告が表示されますが、開発環境のエディターは自分としては編集しづらいので。。。

- SystemVerilog – Language Support – Visual Studio Marketplaceでも、セミコロンとかが抜けてるとメッセージを出してくれます。

Verilog (.v)

- verible Formatterはいい感じに使えそうです。

- Verilog-HDL/SystemVerilog/Bluespec SystemVerilog – Visual Studio MarketplaceのLanguage Supportの機能は使えません。verible-verilog-lsがVerilogでサポートされていないためです。

- SystemVerilog – Language Support – Visual Studio Marketplaceは、セミコロンとかが抜けてるとメッセージを同じように出してくれます。

途中で困ったこと

最初、Verilog-HDL/SystemVerilog/Bluespec SystemVerilog – Visual Studio Marketplaceでverible Formatterの設定をして、VSCodeで使えるようにしていたのですが、なぜかVSCodeでSystemVerilogの既定のフォーマッターとしてこちらを選択すると、インデントがスペース2つ分になってしまう挙動をしてしまいました。

私はインデントはスペース4つ派なので、SystemVerilogの既定のフォーマッターとしてSystemVerilog – Language Support – Visual Studio Marketplaceを設定してverible formatterを使っています。こちらは問題なくインデントがスペース4つ分となりました。

その他気になっているツール等

SystemVerilog Package (Sublime Text)

Sublime Textでは、こういうのもあるみたいなので、試してみたいですね。Sublime Textはあまり使ってこなかったので、使いこなすまでのハードルがあるため、手が出しづらいですが、もしうまく使えそうならSublime TextをHDL記述の専用Editorみたいな感じにするのも良いかも。

少し使ってみた感じだと、スニペットが豊富で、Formatterもあるっぽいです。結構よさそうだった。

VSCodeはスニペットがいまいちな感じがしたので、自分で書いた方がいいかもと思ってます。always_ffとか、ひな形は出してくれるけど、reset_nを非同期で書きたいが、そういうのがないとか。

あと、インスタンスとかも補完があるっぽい。

Verilator

Simulatorがメインのようですが、Lintもできるようです。こちらをLinterとして使ってみたいと思ってます。コマンドラインで使う方法は日本語の記事等少しあったのですが、VSCodeとかのエディター上に表示させる方法とかがうまくわからずに断念しています。

Windowsでの利用について

2024/05/03 追記(記事に頂いたコメントから更新)

verilatorはwindowsにインストールするのが難しいので、WSL (Windows Subsystem for Linux) が必要という旨を教えて頂きました。ありがとうございます。

今後試してみたいと思うので、以下に少し調べたリンクだけ貼っておいて、試せたら更新しようと思います!

Verilator公式

Windowsで動かしてる例

WSLやUbuntuで動かしてる例

HDL Checker

SystemVerilog/Verilogどちらでも、VSCodeの拡張機能でLanguage Serverとして使えるみたいですが、あまり使い方が分からずに断念してしまいました。

2024/05/03 追記(記事に頂いたコメントから更新)

hdl checkerはslangのラッパーなのでどちらかで良いとのことです。

slangについては認識しておらず、LinterやFormatterとして使用できるようですが、veribleやvelilatorとか使ってるなら重複するので、使わなくて良いのかな?と理解してます。

こちらに関しても、理解出来次第追記しようと思います。

おわりに

Pythonとかと比較すると、VerilogとかSystemVerilogとかVHDLとかのHDL言語はこういうFormatterとかLinterとかがエディター上で動かせるのが少ない気がしているので、もっと楽にRTLを書くために今後も調査していこうと思います。(コマンドで実行するとかは有償のLinterとかあるんですが、エディター上で見たいので)

コメント

verilatorはwindowsにインストールするのが難しいので、wslが必要と思います。

wlsから呼び出してlintできます。、

hdl checkerはslangのラッパーなのでどちらかで良いと思います。

コメント頂きありがとうございます。

slangについては全く認識しておりませんでした。

LinterやFormatterとして使用できるようですが、veribleやvelilatorとか使ってるなら重複するので、使わなくて良いのではということですかね。

調べてみて、理解できたら記事の方更新させていただきます!